- Sorry, this product cannot be purchased.

Product Details

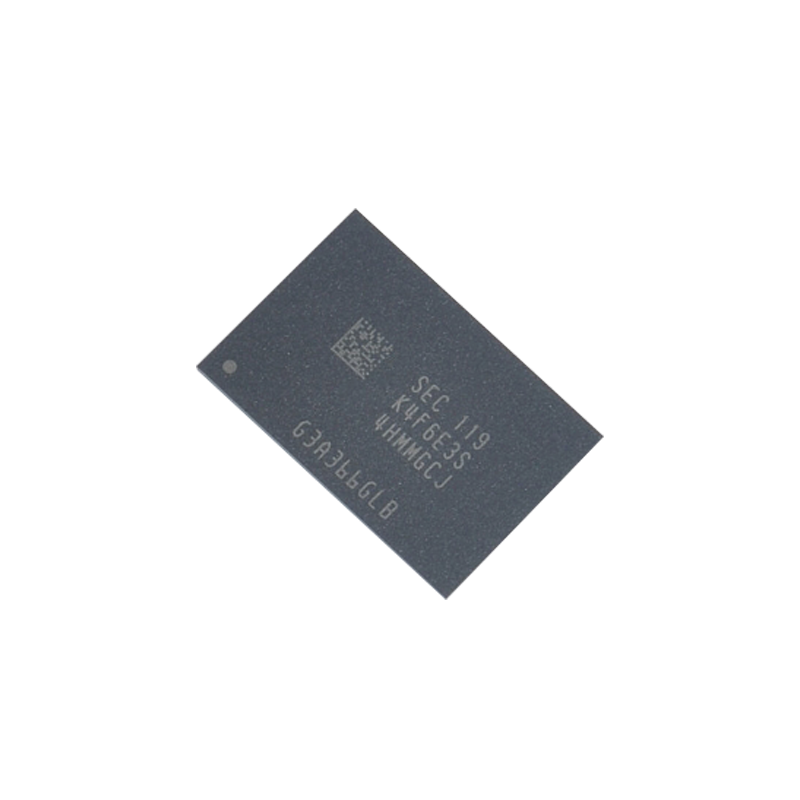

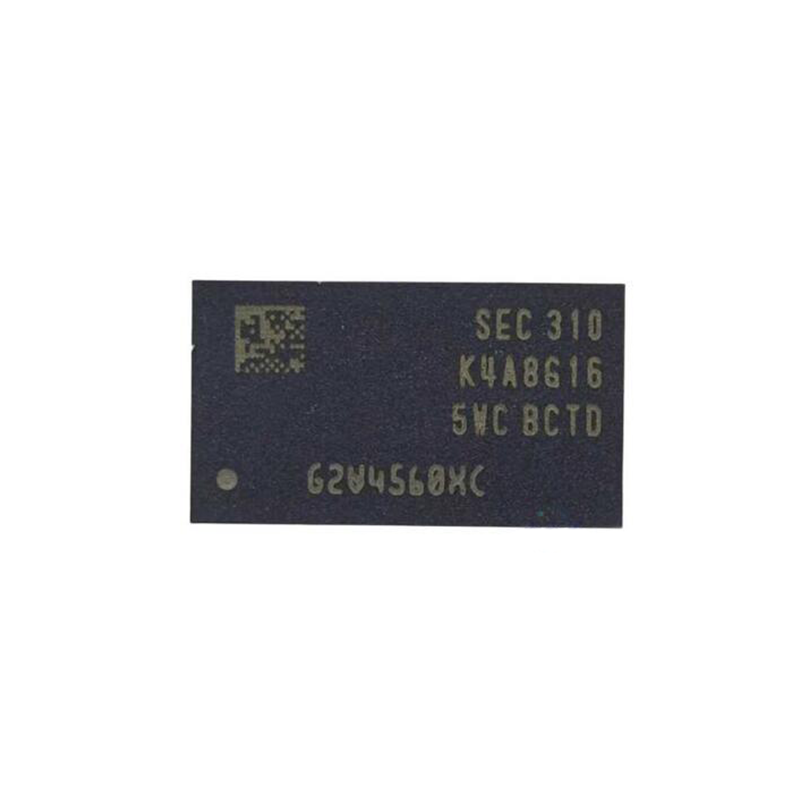

K4A4G165WE-BITD Samsung 4Gb DDR4 SDRAM 96FBGA

Samsung 4Gb DDR4 E-die DDR4 256Mx16 K4A4G165WE-BITD electronic component supplier

• JEDEC standard 1.2V (1.14V~1.26V)

• V DDQ = 1.2V (1.14V~1.26V)

• V PP = 2.5V (2.375V~2.75V)

• 800 MHz f CK for 1600Mb/sec/pin,933 MHz f CK for 1866Mb/sec/pin,

1067MHz fCK for 2133Mb/sec/pin, 1200MHz fCK for 2400Mb/sec/pin,

1333MHz fCK for 2666Mb/sec/pin

• 8 Banks (2 Bank Groups)

• Programmable CAS Latency(posted CAS):

10,11,12,13,14,15,16,17,18,19,20

• Programmable CAS Write Latency (CWL) = 9,11 (DDR4-1600) ,

10,12 (DDR4-1866) ,11,14 (DDR4-2133) ,12,16 (DDR4-2400) and

14,18 (DDR4- 2666)

• 8-bit pre-fetch

• Burst Length: 8 , 4 with tCCD = 4 which does not allow seamless read

or write [either On the fly using A12 or MRS]

• Bi-directional Differential Data-Strobe

• Internal(self) calibration : Internal self calibration through ZQ pin

(RZQ : 240 ohm ± 1%)

• On Die Termination using ODT pin

• Average Refresh Period 7.8us at lower than TCASE 85°C, 3.9us at

85°C < TCASE < 95 °C

• Support Industrial Temp ( -4095°C )

– tREFI 7.8us at -40 °C ≤ TCASE ≤ 85°C

– tREFI 3.9us at 85 °C < TCASE ≤ 95°C

• Asynchronous Reset

• Package : 96 balls FBGA – x16

• All of Lead-Free products are compliant for RoHS

• All of products are Halogen-free

• CRC(Cyclic Redundancy Check) for Read/Write data security

• Command address parity check

• DBI(Data Bus Inversion)

• Gear down mode

• POD (Pseudo Open Drain) interface for data input/output

• Internal VREF for data inputs

• External VPP for DRAM Activating Power

• PPR is supported

Density : 4Gb

Org. : 256M x 16

Speed : 2666 Mbps

Voltage : 1.2 V

Temp. : -40 ~ 95 °C

Package : 96FBGA

The 4Gb DDR4 SDRAM E-die is organized as a 32Mbit x 16 I/Os x 8banks device. This synchronous device achieves high speed double-data-rate transfer rates of up to 2666Mb/sec/pin (DDR4-2666) for general applications.

The chip is designed to comply with the following key DDR4 SDRAM features such as posted CAS, Programmable CWL, Internal (Self) Calibration, On Die Termination using ODT pin and Asynchronous Reset .

All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the crosspoint of differential clocks (CK rising and CK falling). All I/Os are synchronized with a pair of bidirectional strobes (DQS and DQS) in a source synchronous fashion. The address bus is used to convey row, column, and bank address information in a RAS/CAS multiplexing style. The DDR4 device operates with a single 1.2V (1.14V~1.26V) power supply, 1.2V(1.14V~1.26V) V DDQ and 2.5V (2.375V~2.75V) V PP . The 4Gb DDR4 E-die device is available in 96ball FBGAs(x16).